Faced with the daunting challenge of bringing new products to market faster with ever-shorter life cycles, designers are seeking affordable and flexible alternatives to high-cost custom chips. Simply put, traditional ASIC and gate-array solutions no longer cut it, either technologically or economically, in a world in which mask charges have skyrocketed to over $1 million per spin.

In today's uncertain economy, programmable chips are emerging as the product of choice for myriad applications, due to their inherent flexibility, performance, functionality and competitive pricing. In growing numbers, FPGAs are becoming the optimal choice for today's higher volume designs. This trend will accelerate this year with the delivery of Xilinx's Spartan-3 high-density FPGAs, manufactured using the world's most advanced 90 nanometer process technology on 300 mm wafers to further reduce Spartan Series pricing while providing greater functionality,

With up to 5 million system gates and almost 2 million bits of block RAM, Spartan-3 FPGAs compete on both performance and integration levels with traditional custom chips further closing the gap between ASICs and FPGAs. Spartan-3 provides designers with a flexible, low-cost programmable platform for a wide range of high volume applications and includes flexible I/O, embedded high-speed multipliers, and soft processor cores.

Meet the new platform FPGAs

One of the big differences between a traditional logic device and an ASIC is that the term 'system on a chip' historically has been reserved just for ASICs. That position has changed radically now that IP immersion processes are so successful for embedding system component IP into fully programmable FPGA devices. For example, the Xilinx Spartan-3 FPGA integrates block memory, soft microprocessor cores, customisable IP, and high performance DSP functionality into the logic to provide a flexible platform (Figure 1).

The IP-immersion technology from Xilinx allows for integration of system components onto a single device, reducing the total bill of materials parts count, shrinking board space, and improving reliability. With the IP-immersion technology, the hard IP is embedded into the layers of the device, and abundant routing over the IP blocks, allowing high performance and high integration.

Some FPGA vendors are making both soft and hard microprocessors available, so users can craft the solution best suited to their embedded application. Partnering with industry leaders in the microprocessor arena provides popular and mature processor hard cores in a variety of high-performance configurations. You can choose devices that include hard IP processors and can utilise the on-chip memory to guarantee a fixed latency of execution for a higher level of determinism. For example, Xilinx' Virtex-II Pro FPGAs offer a platform for programmable system design with IBM PowerPC processors and multigigabit transceivers immersed into the device. Together with Spartan-3 FPGAs, platform FPGAs address many aspects of reducing system costs. They have similar logic structures, and use the same design tools and IP, but are tuned with different capability/performance tradeoffs. This flexibility and scalability are the direct results of driving Moore's Law to a new level.

Innovative FPGA suppliers have also introduced 32-bit soft microprocessor cores that can standalone or complement hard-core processor applications. You can add soft core computing applications to your platform FPGA designs or, using the same bus standard, introduce soft micro-engines to off-load time consuming functions from the main hard core processor. The soft-core processors do not have the performance of the hard-core types, but they are small and limited only by the size of the FPGA. By supporting both hard- and soft-core processors, an engineering team can create the ideal platform for its specific application.

Ideally, peripherals and other system intellectual property are soft in these programmable platforms, so you can choose exactly what you want and not worry about 'running out' of that IP. Gone are the days of placing additional microprocessor packages on a board - not to use the processor cores themselves, but to supply the required amount of discrete hard IP.

FPGA providers should supply a standard library of IP, including such cores as arbiters, bridges, and UARTs with the device, along with additional high-end cores separately. An additional desired feature is the support necessary for customising the IP to such a detailed level that designers can trade off features, performance and size for every individual piece of IP to enable fine-tuning the entire design

In addition, DSP functionality is exploding in these new platform FPGA systems, in the form of hardwired multipliers that yield hundreds of billions of MAC/s of support. This capability greatly exceeds even the fastest of sequential DSP processors available on the market today. The sweet spot for FPGAs in DSP applications is in the 1 MSPS to 300 MSPS region, where customers are most concerned with high performance and high flexibility.

One of the other key advantages of this new breed of platform FPGAs is flexible connectivity. These FPGAs have to interface to a wide range of products in order to provide a complete design platform. HSTL and SSTL allow efficient memory interfaces, while LVDS provides a high-speed link that avoids cross-talk and other interference. Xilinx Spartan-3 FPGAs offer a platform that provides a flexible connectivity solution. Platform FPGAs offer support for I/O standards and designers can use soft IP building blocks for a wide range of interface protocols such as PCI 32/33 and PCI 64/33, RapidI/O, POS PHY Level 4, Flexbus 4, SPI-4, and HyperTransport.

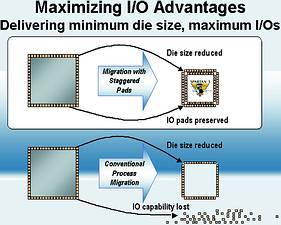

However, the challenge in developing a low cost platform FPGA is to develop a small die to save costs, yet have enough I/O pads around the periphery of the smaller die to offer adequate I/O. Logic IC designers have found a solution with staggered pad technology that implements two rings of I/O pads around the periphery of the die to maintain I/O counts with ever-decreasing die size. One example is the Spartan-3 FPGA, which uses the staggered pad technology (Figure 2).

Appropriate development tools

Platform FPGAs need a full spectrum of development tools, both for design synthesis and for FPGA design compilation, floor-planning, and place-and-route. Vendors need to provide a wide range of partnerships with EDA vendors to support a design engineer's development environment. Furthermore, FPGA design tools need to provide high productivity to minimise design time and design engineering costs.

Incremental design capability slashes design re-compile times by limiting the re-implementation to only the design modules that need to change; the rest of the design is frozen and intact, preserving previous performance results. Modular design delivers a 'divide-and-conquer' team-based approach to high-density design, allowing teams of engineers to complete their modules in parallel, focusing on individual module performance rather than overall design completion, and speeding the design flow through to faster completion. The area mapping capabilities of a floor planner allow for quick-and-easy logic grouping, leading to better timing results, and faster design performance. RPM (relationally placed macros) allow design teams to save away floor planned HDL designs for later design reuse, further increasing productivity. The Xilinx ISE design tools offer a great example of these productivity options.

With Spartan-3 platform FPGAs, engineers will be able to target design modules for silicon hardware in FPGA logic gates or as software applications run on process engines, such as the Xilinx MicroBlaze soft processor. Because many kinds of engineers - hardware, software, firmware, system architects and others -may target these platform FPGAs, look for a 'market leader' tools strategy aimed at appealing to these different camps. Top suppliers not only should produce tools for IP generation, DSP design and logic implementation, but partner with leading EDA and embedded companies to provide best-of-class support for logic synthesis, simulation, co-verification and embedded software development.

For example, by supporting embedded tools from the GNU domain for the Xilinx MicroBlaze soft processor, Xilinx's software strategy should immediately appeal to the largest installed base of embedded users. This will alleviate the issue of design engineers having to embrace completely new development methodologies and will allow them to port existing legacy designs to platform FPGAs. With tens of thousands of educated and trained engineers already using these types of tools, a complementary model is far more constructive than creating a new technology.

Summary

Moore's Law has driven the industry to adopt more and more advanced technologies to deliver higher integration and lower costs. Today, companies can take advantage of low cost, off-the-shelf solutions that provide high integration to get a wide range products to market quickly. These new low-cost platform FPGAs embed hard IP cores, memory, and high-speed I/O with large logic density, to offer a flexible solution that increases design productivity. Imagine how you can use these for the next four decades of system development.

For more information contact Kobus Botes, Memec SA, 011 897 8600, [email protected]

© Technews Publishing (Pty) Ltd | All Rights Reserved