The MIL-STD-1553B bus has been deployed for data communications purposes in civilian and military aircraft since the 1970s. Its major benefit is dual redundant signal paths, which makes it suitable for flight-critical systems.

Although the data transmission rate of 1 Mbps may seem pedestrian in today's world, modern aircraft still have many data communication needs for which 1 Mbps is more than adequate. MIL-STD-1553B cores combined with FPGAs represent a flexible solution to integrate discrete circuits and long lead ASICs into a smaller, lower-power, lower-weight and more-reliable system-on-a-chip.

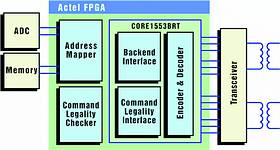

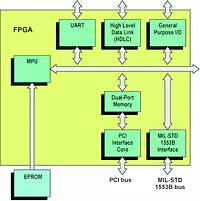

Today, some new aircraft are still using MIL-STD-1553B as a dual-redundant, time-multiplexed serial data bus in low-data rate applications because it is a proven, reliable standard. The fixed solutions that were often used in the past required discrete components in addition to the MIL-STD-1553B remote terminal, bus controller and bus monitor. The more modern solution is to combine a high-reliability MIL-STD-883B, radiation-tolerant or radiation-hardened FPGA with a certified 1553B core along with other components such as a PCI or microprocessor core.

The high costs of buying brand new aircraft has created a substantial market for equipment retrofits to existing aircraft, a process known in aeronautical circles as mid-life upgrades or MLUs. In recent years the advent of new technologies in the fields of displays, radar, communications, flight computers, inertial and GPS navigation, and in-flight entertainment systems has led to operators seeking to upgrade equipment in their fleets. In the military aviation world, changes in aircraft missions since the end of the cold war have combined with new technologies in weapons systems to lead armed forces to seek ways to integrate new equipment into their military aircraft. A MIL-STD-1553B core combined with an FPGA is an excellent way to connect new sub-systems into the aircraft's existing electrical interconnect infrastructure. Replacing, testing and debugging the existing infrastructure would be cost- and time-prohibitive and typically unnecessary considering the data rates of communication do not exceed 1 Mbps.

This poses several problems for system developers. New equipment must:

* Operate with existing infrastructure as well as off-the-shelf standard parts.

* Be flexible to allow sub-system modifications to span multiple aircraft platforms.

* Rapidly come to market with prototypes for quick debugging.

* Reduce power consumption, weight and footprint.

* Avoid the worry of obsolescence.

New equipment will be required to operate with existing equipment and standard parts as the military shifts away from unique ASICs for every application. In this case system developers would typically search for an off-the-shelf standard part to accomplish the function of bridging between 1553 and a commercial interface such as PCI or VME. However, there has historically been very little support from the commercial silicon vendors for 1553 bridging devices because the modest volume of chips does not justify the cost of developing a merchant-market part for each bridging application. Additionally, there is a high probability that each customer will want some unique flavour of intellectual property. For example, customised command sets within a communications protocol or some level of interface multiplexing such as one PCI interface servicing four individual 1553 interfaces.

Upgraded sub-systems are frequently used on multiple aircraft platforms. A fixed silicon chip does not serve multiple platforms nearly as well as an FPGA which can be easily programmed and reprogrammed for multiple board layouts. This reduces the original design time and also reduces the time to build derivative boards and silicon. Thus, the development effort can be amortised across a larger volume of parts due to the economies of scope that are gained from the flexibility of the FPGA architecture. This allows designers to save not only time, but also money, by avoiding the very-large NRE cost and the long debugging period associated with ASICs and mask sets. Prototype FPGA designs can be debugged in the time to build a mask set and wait 12 weeks to fabricate the first silicon, which may or may not work after assembly. Additionally, when problems are found during system integration, a simple change to the FPGA will often fix the problem as opposed to building a new mask and waiting through another fabrication cycle.

A system-on-a-ship FPGA and cleverly-designed intellectual property can substantially reduce the power-consumption, weight and footprint of a PCB. Previous designs used off-the-shelf ASSPs or discrete circuits. One of the problems with these designs was that discrete components all draw significant power as well as take up valuable real estate on a PCB. To be low power, a MIL-STD-1553B core or device should be a state machine that only draws significant power when a state is changed. Microprocessor-based cores and discrete components spend their time processing until they receive an interrupt, then they draw additional energy. Modern design tools make the possibility of using a state machine that does not require constant processing. This significantly reduces power draw. What one needs to do for real-estate considerations is to combine all components into one piece of silicon that is live at power up. This also greatly simplifies the board - a benefit in troubleshooting, cost and time to market.

A final consideration for MIL-STD-1553B is that of obsolescence. Discrete components in MIL-STD-1553B systems are routinely reaching end-of-life (EOL). FPGAs allow designers to avoid their product reaching end-of-life because FPGA vendors have standard products that can be used in a variety of applications. Thus, EOL is delayed due to economies of scope and, when it occurs, the board designer can use the same core in the next-generation FPGA device.

The recent availability of MIL-STD-1553B interface intellectual property, coupled with a burgeoning range of field programmable gate arrays (FPGAs) that offer a variety of screening levels, is helping to solve many problems with existing MIL-STD-1553 systems. Certified MIL-STD-1553B IP is available in netlist and source code form that can be configured by the designer to implement whatever subset or superset of the interface capabilities are desired. The IP comes with a full test bench that enables simulations to be performed, exercising the interface fully to evaluate its response in a variety of scenarios.

FPGAs are available today in a range of temperature and screening levels to suit many applications, from non-flight-critical systems inside the benign environment of an airliner cabin, to weapons systems which must withstand extremes of temperature, humidity, vibration, and other mechanical stresses, and to satellites and space probes where integrated circuits need to be inherently invulnerable to the effects of cosmic radiation.

The use of MIL-STD-1553B IP and high-reliability, robust FPGAs can make the system designer's job of interfacing into a legacy airframe 1553 installation more straightforward, cost effective and timely than any other approach.

For more information contact Kobus van Rooyen, ASIC Design Services, 011 315 8316, [email protected]

| Tel: | +27 11 315 8316 |

| Email: | [email protected] |

| www: | www.asic.co.za |

| Articles: | More information and articles about ASIC Design Services |

© Technews Publishing (Pty) Ltd | All Rights Reserved