At the heart of an ever-increasing number of embedded applications is a processor, so Actel supports embedded systems, designers with a comprehensive portfolio of industry standard processor solutions.

From 32-bit ARM and LEON3 cores to the smallest soft micro available, CoreABC, Actel offers a wide range of processors so that designers can find and use one that closely fits their design needs.

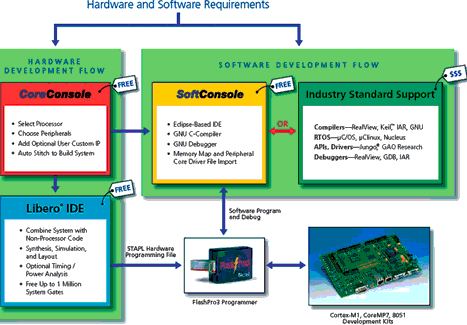

Additionally, Actel offers a comprehensive development environment that includes CoreConsole, SoftConsole, Actel Libero Integrated Design Environment (IDE), boards, and reference designs, in addition to third-party tools and capabilities. This ecosystem of tools and support enables Actel customers to get system-level products to market faster while reducing cost and risk.

Cortex-M1

The Cortex-M1 is a high performance, 32-bit processor developed by ARM in collaboration with Actel for implementation in FPGAs. The first ARM processor developed specifically for FPGAs, it is fast and optimised for size in programmable logic.

Part of the growing ARM family of Cortex processors, the M1 is derived from the Cortex-M3 pipeline. It runs the classic Thumb instruction set allowing existing Thumb code to be run on the processor without change. If users want to move from an FPGA to an ASIC, programs written for Cortex-M1 can be run on Cortex-M3, which can be licensed from ARM for ASIC implementation. This gives users a real path to ASIC implementation, which is not the case with general proprietary 32-bit architectures.

Cortex-M1 has a three-stage pipeline that offers a good balance between size and speed when implemented in an FPGA. The processor runs the ARMv6-M instruction set, and supports instruction and data tightly coupled memories (TCM). It has a configurable nested interrupt controller, optional fast or small hardware multiplier, and can be implemented with or without the debug block. It is available in CoreConsole and connects to the Advanced High Performance Bus (AHB) so designers can build their subsystem and easily add peripheral functionality to the processor.

CoreMP7

The ARM7 is the most widely-used 32-bit RISC microprocessor. Actel's CoreMP7 is a soft IP version of this popular processor that has been optimised to maximise speed and minimise size in Actel M7 Fusion and ProASIC3/E Flash-based devices. With CoreMP7, FPGA users can avoid using proprietary 32-bit processor cores and instead use an industry-standard ARM7 with its well-known architecture and popular instruction set.

CoreMP7 executes the ARMv4T instruction set architecture and implements all

32-bit ARM7 instructions and all 16-bit Thumb instructions. The processor has a

3-stage pipeline, 32-bit ALU, 32-bit register file, a JTAG debug interface, and includes a configurable AHB interface wrapper that can be used to connect the native ARM7 bus to an on-chip AHB interconnect bus.

Actel M7 FPGAs have all the features of other Actel Flash family devices and have been enabled for seamless use of CoreMP7. These devices are based on nonvolatile Flash technology and support 250 000 to 3 million gates and up to 616 high performance I/Os.

Core8051/Core8051s

The 8051 continues to win new designs because it is an industry standard architecture with a huge range of available code, a large assortment of tools, and a vast number of designers who have used it. Whenever an application requires a small, low power, control element, the Actel Core8051 or Core8051s is a good choice. Both cores are available for free, they are fast, supported by a full set of development tools, and have been optimised for Actel FPGAs.

* Core8051 can be implemented using a netlist or RTL and is 8051-compatible, so designers can take advantage of the huge body of existing code to shorten their design time. Core8051 has an 8-bit ALU and standard 8051 features, including Special Function Register and memory interfaces, and power management circuitry.

* Core8051s is an implementation of the 8051 architecture with all of the peripheral functions removed and an Advanced Peripheral Bus (APB) interface added to the SFR interface. This allows designers to easily connect any APB peripheral IP function, and configure the core specifically to meet their application needs. Core8051s is also fast and can run existing 8051 code, and works with the existing 8051 development tools.

The debug blocks on Core8051 and Core8051s are identical, so the same tools can be used for both cores. Actel has a number of kits that can be used to develop and prototype their designs. These include the System Manager board or Fusion Starter Kit for Fusion devices, the CoreMP7 board for ProASIC3/E devices, Platform8051 Development Kit for ProASICPLUS, and the Axcelerator Starter Kit for Axcelerator devices.

CoreABC: smallest soft micro

Actel's CoreABC is the smallest and first RTL-programmable soft micro available for FPGAs and can be used to implement a broad range of embedded applications. The free controller can be implemented in as few as 241 tiles and without RAM or ROM resources, so designers can use CoreABC in the smallest Actel devices, including the low-cost A3P030 ProASIC3 device.

CoreABC is available in CoreConsole and highly configurable so it can be tailored to support custom data types or data path widths. The core uses a programmable sequence controller that enables targeted local control of embedded functions. The processing unit can store and test data, allowing read/write cycles to be varied dynamically. CoreABC is programmed by assembly-type instructions that can be stored either in hardware gates or memory. When a small number of instructions are required, RTL programming offers advantages. Alternatively, running CoreABC from memory enables more efficient programming when a larger number of instructions is needed. CoreABC can be used as the main processor in simple control applications or for distributed control within a large system implementation.

This small, soft micro can be used with Actel Flash-based Fusion and ProASIC3 families, or any of the antifuse families, including RTAX-S and Axcelerator.

For 'system-critical': LEON3

LEON3 is a 32-bit processor that is compliant with the SPARC V8 architecture, and has been optimised for use in Actel FPGAs. It can be used with high-end operating systems such as MS Windows and Linux. The full source code for LEON3 is available under the GNU GPL licence. The processor is also available under a low-cost commercial licence from Gaisler Research. A fault-tolerant version of the LEON3 processor is also available for system critical applications.

Processor design flow and tools

Major benefits for users of industry-standard microprocessors for use with Actel devices are the huge ecosystem of tools and design support and the large volume of embedded software programs that exist for them. To this ecosystem, Actel adds the CoreConsole IP Deployment Platform (IDP), SoftConsole, Libero IDE, and a complete development and debug environment.

Actel processor users can shorten their development time using CoreConsole, an intellectual property deployment platform that includes a graphical user interface and a block stitcher to simplify the assembly of IP cores for embedded applications in FPGAs. This tool integrates with Actel Libero IDE, which includes place-and-route synthesis and simulation tools. The Actel SoftConsole program development tool suite provides tools for building, debugging, and managing software development projects that run on the processors. SoftConsole has an easy-to-use interface, and contains a C compiler and debugger for each of the processors.

For programming, the FPGA fabric on Actel devices, including the M7 and M1 devices, can be programmed and debugged with the Actel FlashPro3 programmer. All Actel Flash-based devices support in-system programming (ISP) with the programming data supplied through a standard JTAG interface from FlashPro3 or a microprocessor.

Development kits

The CoreMP7 and system management development kits are complete prototyping and evaluation packages consisting of a board with an M1 or M7 device, Actel Libero IDE Gold, CoreConsole, SoftConsole, an optional FlashPro3 programmer with a USB cable, a power supply and tutorials. These kits can also be used for development of systems with Core8051, Core8051s, or CoreABC. In addition, Actel has many other development kits that can be used with these cores, so designers can develop applications and explore the benefits of all of the Actel industry standard processors in Actel FPGAs.

AMBA to tie it all together

An important set of functional blocks used with a microprocessor is the subsystem peripherals. These include all of the low level functionality that must be implemented around the processor so it can be used in an application. To make designing with processors easier, Actel supplies a full range of subsystem peripherals, including an AHB bus interface, APB bus interface, AHB to APB bridge, memory controller, interrupt controller, timers, serial interface, buffered I/O interface, and many other functions. All of these subsystem peripherals connect to the processor with the AMBA bus and are delivered free as part of the CoreConsole IP Deployment Platform (IDP).

| Tel: | +27 11 315 8316 |

| Email: | [email protected] |

| www: | www.asic.co.za |

| Articles: | More information and articles about ASIC Design Services |

© Technews Publishing (Pty) Ltd | All Rights Reserved