In undersampling applications, including wideband receivers, cellular base stations and communication receivers, the undersampled signal has a relatively low bandwidth.

However, the carrier frequency associated with this signal is high enough for timing inconsistencies, such as clock jitter (or phase noise) and A/D converter aperture jitter, to increase noise as the signal passes through the A/D converter. Large amounts of jitter can make the A/D converter block unusable for this type of system.

There are three main noise sources in this type of application: quantisation noise of the converter (or the AC differential non-linearity error), the internal converter thermal noise and the system jitter. The converter quantisation noise and thermal noise have a direct effect on the signal-to-noise ratio (SNR) of the converter, but the only means of controlling them is by careful selection of the converter.

The system jitter comprises the aperture jitter of the sample-hold switch at the input of the A/D converter, and the sampling clock jitter. Aperture jitter is the sample-to-sample variation timing of the input switch of the A/D converter. This specification can be found in the product data sheet. Clock jitter is an artefact of clock variation from cycle to cycle. These two uncorrelated jitter noise sources should be combined using the root-sum-square formula, or tJITTER = (tJCLOCK² + tJADC²) in psRMS, where tJITTER is the total jitter of the system, tJCLOCK is the jitter from the external A/D converter clock and tJADC is the jitter of the A/D converter input sampling switch.

It is not possible to change the application circuit to improve the aperture jitter of the converter. However, the clock jitter can be improved by using one of several techniques.

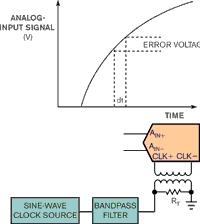

In a typical application, the external clock controls the sampling frequency or speed of successive conversions. Assuming that there are no phase shifts in the analog input signal, clock jitter causes sampling time uncertainty (Figure 1). This uncertainty affects the SNR of the conversion. The theoretical impact on SNR, due to jitter from the clock as well as jitter from the A/D converter sampling mechanism, is SNR (dBc) = -20 log10 (2π fIN tJITTER), where fIN is the analog input frequency.

A clock with low jitter or phase noise is therefore needed to drive the A/D converter in undersampling systems. The clock can be digital or sinusoidal, each offering its own advantages and disadvantages. Digital clocks have a very fast slewing transition, which helps to reduce clock jitter, but the fast edges of these clocks create wideband noise that is aliased back into the signal bandwidth. A sinusoidal clock may be a suitable alternative, depending on the application and layout, but most have higher rms near-band jitter. Most A/D converter data sheets provide clock recommendations.

Another choice to be made for most undersampling A/D converters is between differential and single-ended clock inputs. Single-ended clocks must have a clock slope of about 1 V/ns or better, so they are not suitable for sine-wave clocks. Also, the voltage swing of the single-ended clock must be limited to avoid the clock signal bumping into supply rails, turning on internal protection devices. Differential clock signals double the voltage range of the clock. The converter also does some common-mode rejection of noise signals.

It is important to take clock phase noise or jitter into account when planning a clock strategy for an undersampling A/D converter. The chosen clock source need not be expensive, but should be low noise.

For more information contact Arrow Altech Distribution, +27 (0)11 923 9600, Avnet Kopp, +27 (0)11 809 6100, Electrocomp, +27 (0)11 458 9000, Future Electronics, +27 (0)31 262 7743 or Tempe Technologies, +27 (0)11 452 0530.

| Tel: | +27 11 458 9000 |

| Email: | [email protected] |

| www: | www.electrocomp.co.za |

| Articles: | More information and articles about Electrocomp |

| Tel: | +27 11 923 9600 |

| Email: | [email protected] |

| www: | www.altronarrow.com |

| Articles: | More information and articles about Altron Arrow |

| Email: | [email protected] |

| www: | |

| Articles: | More information and articles about Tempe Technologies |

© Technews Publishing (Pty) Ltd | All Rights Reserved