Programmable ASSP provides enhanced flexibility for high-speed designs

4 July 2001

Programmable Logic

Altera offers a new level of system integration with its Mercury device family. Said to be the world's first programmable ASSP, Mercury devices combine the high-speed I/O capabilities of an advanced clock data recovery (CDR)-enabled transceiver with a performance-optimised core that is built for bandwidth. This high performance I/O support enables systems in backplane, chip- to-chip, and line-side applications via support for a variety of I/O protocols including Gigabit Ethernet and SONET/SDH.

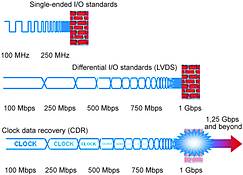

Figure 1. The need for CDR at speeds of 1 Gbps and beyond illustrated: CDR removes clock skew concerns by encoding the clock into every data stream, guaranteeing that the clock and data are always perfectly in phase. This eliminates tight routing signal requirements, removing the need for a specified layout relationship between the clock and data lines

The CDR transceivers within the Mercury devices eliminate frequency barriers faced by source-synchronous systems by offering data rates of up to 1,25 Gbps and a total CDR bandwidth of up to 45 Gbps. This advanced CDR capability, combined with a high performance core and distributed multiplier capability, offers system designers an effective solution for key communications applications.

These standards are implemented with the flexibility of programmable logic. Mercury CDR supports up to 18 channels per device, each capable of up to 1,25 Gbps operation. The Mercury device family also supports a variety of high-speed I/O standards, external memory interfacing, enhanced phase-locked loops (PLLs), and quad-port capable embedded system block (ESB) RAM, giving customers the possibilities of ASSPs in a programmable logic device.

The Mercury devices offer support for a wide variety of common protocols, including SONET, Gigabit Ethernet, RapidIO, POS-PHY Level 4, IEEE-1394 and Fibre Channel. This support is enabled with the LVDS, LVPECL and PCML physical standards.

The Altera Mercury family consists of two 1,25 Gbps devices: EP1M120 with 8 CDR channels containing 120 000 gates of programmable logic and EP1M350 with 18 CDR channels, containing 350 000 gates of programmable logic.

Further reading:

Solving industry 4.0 challenges with software-configurable I/O

Altron Arrow

Programmable Logic

Software-configurable I/O modules solve problems caused by connecting legacy equipment to modern Ethernet controllers by allowing for the efficient use of all channels in an I/O system.

Read more...

Rapid prototyping with new Xilinx FPGA evaluation kit

EBV Electrolink

Programmable Logic

Equipped with the Xilinx Spartan-7 FPGA, the kit is built for rapid prototyping of industrial networking, embedded vision and automotive designs.

Read more...

Embedded vision development tool for RISC-V FPGA

EBV Electrolink

Programmable Logic

Microchip Technology announced the second development tool offering in its Smart Embedded Vision initiative for designers using its PolarFire RISC-V system-on-chip (SoC) FPGA. The industry’s lowest-power

...

Read more...

Latest updates to Libero SoC v2021.3 Design Suite

Altron Arrow

Programmable Logic

Microchip Technology recently introduced new MPFS025T/095T/160T/250T PolarFire SoC devices with Tgrade2 operating conditions in standard and -1 speed grades and MPFS095TS/250TS/460TS devices with MIL

...

Read more...

HLS tool suite for PolarFire FPGAs

EBV Electrolink

Programmable Logic

The need to combine performance with low power consumption in edge compute applications has driven demand for field programmable gate arrays (FPGAs) to be used as power-efficient accelerators while also

...

Read more...

Mid-range FPGAs for edge compute systems

Avnet Silica

Programmable Logic

Edge compute systems need compact programmable devices with low power consumption and a small enough thermal footprint to eliminate fans and other heat mitigation while providing robust compute horsepower.

...

Read more...

Microchip achieves JEDEC qualification for rad-tolerant FPGA

Future Electronics

Programmable Logic

Developers of small-satellite constellations and other systems used in ‘New Space’ missions must deliver both high reliability and radiation protection while meeting stringent cost and scheduling requirements.

...

Read more...

Intel Agilex FPGAs deliver flexibility and agility for the data-centric world

Altron Arrow

Editor's Choice Programmable Logic

The Agilex FPGA fabric and innovative chiplet architecture delivers an extensible FPGA platform that scales across a wide range of device densities and brings key features and benefits to the table.

Read more...

Security tool for mission-critical FPGAs

Future Electronics

Programmable Logic

Mission-critical and other high-assurance systems deployed worldwide are under rapidly evolving threats from cybercriminals who attempt to extract Critical Program Information (CPI) via the FPGAs that

...

Read more...

Lattice releases new version of sensAI

Future Electronics

Programmable Logic Design Automation

New enhancements have been made to Lattice Semiconductor’s award-winning sensAI solution stack for accelerating AI/ML (artificial intelligence/machine learning) application development on low-power Lattice

...

Read more...