Solution for synchronising multiple direct digital synthesizers

22 May 2002

DSP, Micros & Memory

The fast frequency hopping, extreme tuning resolution, and programmable phase control attributes of direct digital synthesizers (DDSs) make them a compelling choice for a wide variety of signal synthesis applications. However, many applications, such as phased-array radar and critical timing generators, require precise phase-synchronisation of multiple synthesized output signals. Phase synchronisation of multiple synthesizers is a challenge for PLL and other traditional analog-based architectures.

The AD9852/9854 and AD9850/9851 DDS devices from Analog Devices, with up to 14 bits of programmable phase-offset resolution (for AD9852/9854), provide an easy and precise solution for phase synchronisation of multiple synthesized signals. The synchronisation of multiple DDS devices is accomplished as follows.

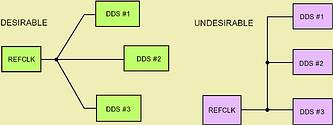

There are two basic timing requirements to be met in order for successful synchronisation to occur. The first, and somewhat obvious, is a coincidental REF clock between all DDSs. Coincidental means that the REF clock pins of each DDS have REF clock timing coincident in time (Figure 1). This is accomplished through proper PCB layout.

Figure 1. PCB layout must ensure that REFCLK edge arrives coincidentally at clock input pins of multiple DDSs

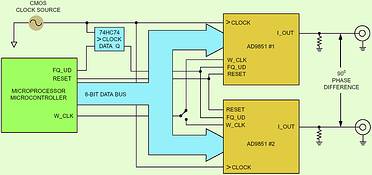

The second timing requirement between all DDS devices is the coincidental transfer of the programmed input data to the DDS core. Performing this transfer are two key signals: FQ_UD for the AD9850/9851 and I/O update clock for the AD9854/9852. If the rising edges of these two signals are sent synchronously to the multiple DDSs, along with proper set-up time relative to the REF clock, then synchronisation will be achieved (Figure 2).

Figure 2. Dual AD9851 set-up for quadrature output

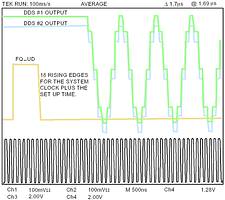

With proper procedure, synchronisation can be readily achieved among multiple DDSs; Figure 3 illustrates synchronisation of two AD9851 devices. In this case, the REFCLK frequency is set to 10 MSa/s. Synchronisation is also achievable up to the maximum system clock rate (including PLL mode).

Figure 3. DDS synchronisation (conditions: VCC = 5 V, REFCLK = 10 MSP, nonPLL mode, 25°C)

Typical applications are for clock synthesis, ADC encode generators, and agile local oscillators.

Further reading:

The end of ‘entry-level’: STMicroelectronics’ STM32C5 sets a new baseline for embedded systems

DSP, Micros & Memory

[Sponsored] Instead of incrementally improving legacy Cortex-M0+ architectures, STM32C5 introduces a Cortex-M33-based platform into the entry-level category. This changes not only performance expectations, but also how engineers approach system architecture, consolidation, and long-term scalability.

Read more...

GigaDevice expands GD25UF Series density

NuVision Electronics

DSP, Micros & Memory

GigaDevice has announced the expanded density range of its GD25UF series 1,2 V ultra-low power SPI NOR Flash, now spanning from 8 Mb to 256 Mb.

Read more...

ARINC 429 line driver evaluation board

ASIC Design Services

DSP, Micros & Memory

Holt Integrated Circuits have announced the release of the ADK-85104 Evaluation Board, a compact, ready-to-use platform designed to help engineers rapidly evaluate and characterise Holt’s HI-85104.

Read more...

Highly integrated 24-channel mixed signal IC

EBV Electrolink

DSP, Micros & Memory

Microchip Technology has announced the LX4580, a 24-channel mixed-signal IC designed to replace multiple discrete components with a single device that supports synchronised data acquisition, fault monitoring, and motor control.

Read more...

Lower-power Thread and BLE connectivity

iCorp Technologies

DSP, Micros & Memory

Espressif has released the ESP32-H21, a low-power wireless SoC aimed at Thread, Matter, Zigbee, and Bluetooth LE device designs.

Read more...

Touch-enabled 32-bit MCU

EBV Electrolink

DSP, Micros & Memory

Microchip’s PIC32CM PL10 microcontroller family expands the company’s Arm Cortex-M0+ portfolio, delivering a compact, low-power 32-bit platform designed for cost-sensitive embedded applications.

Read more...

Build smarter with UNO Q

Electrocomp Express

DSP, Micros & Memory

The Arduino UNO Q’s hybrid design combines a Linux Debian-capable microprocessor with a real-time STM32U585 microcontroller making it the perfect dual-brain platform for the next innovation.

Read more...

Compact AI modules for imaging

Otto Wireless Solutions

DSP, Micros & Memory

SIMCom has introduced two compact smart AI modules, the SIM8666 and SIM8668, designed to simplify the development of imaging-based IoT applications.

Read more...

Compact Renesas MCU rapid development board

Dizzy Enterprises

DSP, Micros & Memory

Built around the Renesas R7FA4M2AD3CFP microcontroller, the Clicker 4 board provides engineers with a ready to use solution for prototyping and testing applications that require reliable ARM based processing and flexible expansion.

Read more...

IO Ninja and Python working hand-in-hand

RF Design

DSP, Micros & Memory

IO Ninja is a professional all-in-one terminal emulator, sniffer, and protocol analyser that runs natively on Windows, Linux, and macOS, and excels as a UI debugger for serial, network, USB, and all other forms of communication.

Read more...