Analog Devices' most advanced 16-bit DSP core architecture is at the heart of the Blackfin processor. This core, a joint development between ADI and Intel, has three primary objectives which are: high performance; dynamic power management; and ease of use.

The Blackfin is targeted at applications like: automotive; broadband access; central office/network switch; digital imaging; GPS; industrial signal processing; instrumentation/telemetry; Internet appliances; POS terminals; etc.

The Blackfin processor's core performance and architectural partitioning allows for development of a complete, high performance DSP system that could incorporate either ADI's VisualDSP Kernel (VDK) RTOS or many other industry recognised realtime operating systems - all within a single processor environment. Low latency realtime DSP code can be run on the Blackfin processor and enhanced by using the expandability and flexibility of VisualDSP Component Software Engineering (VCSE) capabilities. This is offered in VisualDSP++ for Blackfin processors. Additionally, higher latency control tasks can be simultaneously scheduled and executed, allowing the Blackfin processor to be at the heart of many embedded systems.

Memory optimised and configurable

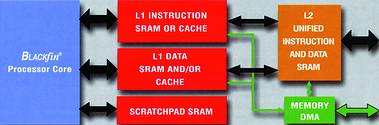

The Blackfin processor core is a highly parallel, fully interlocked pipeline architecture that allows users to achieve the most work possible per cycle. To complement this, it uses a very powerful and flexible L1 and L2 memory hierarchy. Both L1 instruction and data memories can be dynamically configured as SRAM, cache, or a combination of both - all depending on how the processor core is to be used for the given task. Blackfin processors can also include an integrated, unified instruction and data L2 SRAM for larger storage needs. Both the L1 and L2 memories are dual-ported so that information can be simultaneously incoming and outgoing for maximum throughput with minimal core processor impact.

These processors also use Dynamic Power Management that controls critical power consumption and performance parameters. It allows designers to fully optimise the design for the intended application. They are designed to achieve the most work per cycle to maximise the computational processing power per required mW. Applications may independently vary both frequency of operation and voltage of operation of the processor core, resulting in significantly lower overall power consumption.

System integration

The ADSP-BF535 is a highly integrated system-on-a-chip (SoC) solution intended for next generation digital communication and connected media applications. By combining industry-standard communication interfaces with a high performance processor core, OEMs can develop cost-effective solutions quickly and effectively without the need for costly external components. System peripherals include UARTs, SPIs, serial ports, general-purpose timers, a realtime clock, watchdog timer, USB device, and PCI bus interfaces for further peripheral expansion. Other Blackfins include the 750 MHz ADSP-BF533 and the ADSP-BF561 which integrates two Blackfin cores.

Support tools

Blackfin processors are supported by ADI's Crosscore development tools, which include the industry-leading VisualDSP++ development environment, evaluation kits, and emulators. The VisualDSP++ environment consists of a full range of tools such as a C/C++ compiler, linker, debugger, simulator, statistical profiling, and the VisualDSP++ kernel. The EZ-KIT Lite evaluation system helps begin application development. ADI emulators, among other tasks, allow one to load code, set breakpoints, observe variables, observe memory, and examine registers. ADI also has a large third-party development community - the DSP Collaborative - supporting signal processing applications.

© Technews Publishing (Pty) Ltd | All Rights Reserved