Power sequencing and management is a targeted application space for Actel's Fusion programmable system chip (PSC) - the world's first mixed-signal FPGA. As the ultimate PSC, Fusion integrates configurable analog, Flash memory, and FPGA fabric in a monolithic PSC.

Coupling Fusion with Actel's Core8051 or CoreMP7 (an optimised soft-core ARM7 implementation) and CoreAI (Analog Interface) opens new doors in the power management sector by combining the benefits of both programmable logic and embedded processing in a single chip. Supporting both SRAM and embedded Flash memory, the Fusion PSC is the only single-chip soft processor platform, reducing cost and simplifying board design.

Fusion leverages the Actel Libero integrated development environment (IDE) and CoreConsole, the Actel IP deployment platform (IDP) responsible for providing IP (CoreMP7 and CoreAI) and system stitching. CoreAI allows the user to treat the Fusion analog peripherals as peripherals of the microprocessor, thereby allowing the processor to configure and control the analog functions explicitly and providing the capability to customise the system for specific applications.

Fusion supports the following power control functions:

* Power sequencing: controls ramp-rate and timing; customises voltage thresholds; reconfigures power sequence; provides a clean power-up profile.

* Power management: monitors analog voltage, current, and temperature; flags over/under voltage, current, and temperature thresholds; provides system protection based on threshold flags; controls power ramp-up and shutdown.

* Power-on/brownout reset: detects power-on and brownout conditions; resets user logic or an external system.

Minimising power consumption is becoming a more important aspect of system design, from battery-operated devices to rack-based environments. In order to meet this need, the Fusion PSC was developed to have an internal voltage regulator, allowing it to operate from a single 3,3 V supply.

A voltage regulator, realtime counter (RTC), crystal oscillator circuit, and RC oscillator are all integrated, allowing Fusion to support several low power modes of operation. Fusion can power down the core and wake-up at regular intervals programmed into the RTC. Offering further power savings, the RTC and crystal oscillator can be turned off. In this state, an external stimuli (much like a microprocessor interrupt) can wake the device.

System overview

Fusion makes an excellent system master because it operates from a single 3,3 V supply, and it is a Level 0 live at power-up (LAPU) device (for more information, see 'Live at Power-Up': www.actel.com/documents/LAPU_WP.pdf). Fusion can monitor, sequence, and manage several power supplies. With CoreMP7 or Core8051 it can communicate the sampled values to other external systems via RS232, RS485, 10/100 Ethernet, and/or other user-implemented interface, or charge batteries with a pulse width modulation (PWM) peripheral.

Application details

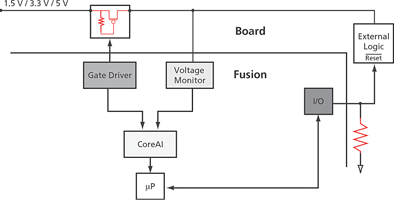

Fusion analog I/Os are arranged in an analog quad configuration: three inputs matched with a metal-oxide semiconductor field-effect transistor (MOSFET) gate driver. Fusion devices support between five and 10 analog quads. Each quad can easily monitor supply or load side voltage, current, and temperature. The gate driver output provides adjustable control of an external power MOSFET with either ramp-rate control or voltage potential control. These can be used for power sequencing and load-side voltage and/or current protection. Figure 1 details a power management system implemented in a Fusion device (pin AT9 is used as a voltage monitor channel in this example).

Power-up sequencing

A microprocessor-enabled Fusion FPGA can be configured as a system supervisory device that continuously monitors all power supplies. When power supplies reach user-defined threshold values, Fusion can enable the pass MOSFET to provide power to the load device. Power-up sequencing is provided either by ramp-rate control or by voltage monitoring.

To use ramp-rate control, the user must set the drive strength of each MOSFET gate driver. The ramp-rate is derived from the different loads and their voltage threshold, which provides a clean ramp-up profile. Using voltage monitoring, the user must define the turn-on condition for a power supply based on the condition of another supply. For example, the user turns on a 1,5 V power supply only when the 3,3 V supply exceeds 3,275 V. Timing and logic for power-up sequencing is implemented by the user as application code executed on the embedded microprocessor, and is therefore completely configurable by the user.

Power management

After the power MOSFETs are enabled, the embedded microprocessor in Fusion monitors voltage on both the supply and load side. Further, the current flowing to the load is monitored to ensure acceptable operating conditions. The microprocessor application compares the realtime voltage and current values to user-configured preset thresholds and sends alerts when applicable. The application can also disable the corresponding MOSFETs to protect the load side devices when the voltage and/or current are outside acceptable operating conditions. The application would then re-enable the MOSFETs when the voltage and/or current return to acceptable levels. A statistical profile of each power supply, including information such as voltage and current values, over limit alerts, and turn-on/turn-off times, can all be recorded within the Fusion device using the embedded Flash memory.

Power-down sequencing

An embedded microprocessor in Fusion can handle not only power-up sequencing but also turning off power supplies based on triggers from internal or external events. Before turning off the corresponding supplies, the microprocessor application can record the status of each supply in the embedded Flash memory for later analysis.

Power-on/brownout reset

Fusion can generate a reset to other devices on a system or respond to brownout conditions. In the example shown in Figure 2, Fusion sends a reset signal to the embedded processor (and/or external logic) through a standard FPGA I/O as it applies power during system power-up. An embedded processor in Fusion can also assert a reset signal whenever a power supply drops below a programmable threshold voltage (as set by the user). The reset signal would then be held asserted for a specified period of time after the supply had risen above the user-defined threshold.

Conclusion

An Actel Fusion device coupled with an embedded soft-core microprocessor has all the features needed to implement a sophisticated power sequencing and management system. It is capable of monitoring voltage, current, and temperature, and has MOSFET gate drivers. The embedded Flash memory, Flash-based FPGA fabric, and soft-core microprocessor enable a simple and complete single-chip solution. The easy-to-use CoreConsole tool along with its IP allows customers to implement their applications quickly and easily. With all these features tied to Flash FPGA logic, the power management system can be completely customised by the user, offering flexibility unmatched by any other power management control solution on the market today.

| Tel: | +27 11 315 8316 |

| Email: | [email protected] |

| www: | www.asic.co.za |

| Articles: | More information and articles about ASIC Design Services |

© Technews Publishing (Pty) Ltd | All Rights Reserved