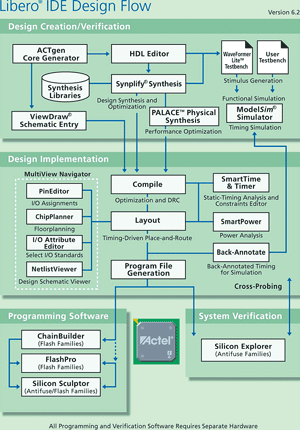

Detailing significant new functionality for design analysis and timing closure, Intel claims its new Libero Version 6.2 Integrated Design Environment (IDE) integrates best-in-class design tools to enable field-programmable gate array (FPGA) designers to achieve the highest results in terms of quality, efficiency and functionality.

In Libero 6.2, Actel has included a new SmartTime static timing analysis environment, enabling customers to analyse and manage timing constraints, perform advanced timing verification, and ensure predictable timing closure through a tight integration with timing-driven place and route.

In this edition of Libero, Actel and Mentor have extended their partnership to provide Mentor Graphics' ModelSim AE simulation as an integral part of the Libero 'Gold' package, which is now available to all Actel customers free of charge. In addition, Version 6.2 includes enhanced synthesis capabilities from Synplicity and physical synthesis features from Magma Design Automation. Further, Libero now runs on Linux and Solaris platforms.

SmartTime

SmartTime is a powerful new multiview product that Actel developed to help designers perform detailed timing analysis and quickly determine the steps necessary to achieve design closure. The SmartTime Constraints Editor view enables users to list, edit and create precise timing constraints. It includes a graphical user interface with visual dialogues that guide users toward capturing their timing requirements and timing exceptions correctly.

Another view, the SmartTime Analyser, allows designers to perform per-clock-domain minimum and maximum timing analysis, and provides inter-clock domain analysis capabilities. The tool simplifies the analysis process by enabling designers to track paths with timing violations quickly. Designers can then directly set specific timing exceptions on the violating paths to tighten or relax the requirements and quickly iterate toward timing closure.

Mentor Graphics' ModelSim is a leading Windows-based simulator for VHDL, Verilog or mixed-language simulation environments. The integrated ModelSim verification and debug environment, to help designers locate bugs faster, is being offered with unlimited availability to all Actel customers for the first time.

Tools support

Synplicity's Synplify FPGA synthesis software offers a new capability to forward-annotate Synopsys Design Constraints (SDC) and physical constraints, enabling the Libero 6.2 IDE to import user-defined constraints automatically then manage, track and pass them forward to design implementation, enabling designers to quickly meet timing closure. In addition, the software now includes critical path resynthesis to improve quality of results for designs based on Actel's Axcelerator family of FPGAs. Magma Design Automation's Palace physical synthesis software now also provides support for Actel's Axcelerator family.

| Tel: | +27 11 315 8316 |

| Email: | [email protected] |

| www: | www.asic.co.za |

| Articles: | More information and articles about ASIC Design Services |

© Technews Publishing (Pty) Ltd | All Rights Reserved