Actel’s new IGLOO family of reprogrammable, full-featured Flash FPGAs is designed to meet the demanding power and area requirements of today’s portable electronics. Based on the company’s nonvolatile Flash technology and single-chip ProASIC3 FPGA architecture, the 1,2/1,5 V operating voltage family now offers the industry’s lowest power consumption.

Actel's proprietary Flash*Freeze technology used in IGLOO devices enables easy entry and exit from the ultra-low power mode, which consumes as little as 5 μW, while retaining SRAM and register data. Flash*Freeze technology simplifies power management through I/O and clock management without a need to turn off voltages, I/Os, or clocks at the system level. The IGLOO family also supports secure in-system reprogrammability, which allows quick and easy upgrades or design updates in the final stages of manufacturing or in the field.

The IGLOO family supports up to 3 million system gates with up to 504 Kbits of true dual-port SRAM, up to six embedded PLLs, and up to 616 user I/Os. The devices are offered in a small form factor (8 x 8 mm), high-density (196-pin), chip scale package and a quad flat package (132-pin).

Extending battery life

The IGLOO family is designed to maximise usable power in many different ways. In Flash*Freeze mode, power drops to as low as 5 μW and no additional components are required to turn off I/Os or clocks while preserving the design information, SRAM content, and registers. Entering and exiting Flash*Freeze mode takes less than 1 μs.

Additionally, the Low Power Active capability (static idle) allows for ultra-low power consumption (from 25 μW) while the IGLOO device is completely functional in the system by maintaining I/Os, SRAM, registers, and logic functions. This allows the IGLOO device to control the system power management based on external inputs (eg, scanning for keyboard stimulus) while consuming minimal power.

In sleep mode, larger IGLOO FPGAs experience maximum power savings when the FPGA core voltage is powered down. The unique Level-0 live at power-up (LAPU) capability of Actel Flash devices allows for rapid system wake-up from sleep mode.

Actel IGLOO FPGAs are the only 1,2 V low power programmable logic devices (PLDs) and consume 30% less static power and over 50% less dynamic power than traditional 1,8 V 'low power' PLD alternatives. IGLOO 1,2 V operation often eliminates an additional DC-DC power converter for the 1,8 V power rail, saving power, area, and cost. Flash-based IGLOO devices also do not suffer from high inrush current at start-up or battery-sapping configuration current each time the system is powered up. Having a true ASIC-like power profile enables the IGLOO FPGAs to dramatically extend battery life relative to SRAM and Hybrid PLD alternatives.

Features/benefits

Flash-based Actel IGLOO FPGAs are full-featured and include clock conditioning analog PLLs for clock generation, on-chip SRAM, and nonvolatile user memory storage, all of which help eliminate parts and reduce total system power consumption and cost. They are ideal for next-generation handheld systems such as smartphones and portable media players. Additionally, available targeted reference designs speed product development for many portable applications.

Being true single-chip devices, the Actel IGLOO FPGAs do not require configuration or other support components, and offer a variety of small footprint packages with high I/O pin count to match design needs. Like a digital ASIC, nonvolatile Flash-based IGLOO devices have the advantage of being a secure, low power, single-chip solution that is Level 0 LAPU. Unlike ASIC devices, the IGLOO devices are reprogrammable and offer time to market benefits. This allows users to quickly and easily upgrade and update the design in the final stages of manufacturing or in the field without non-recurring engineering (NRE) charges and at an ASIC-level unit cost.

Mass storage solution for portable devices

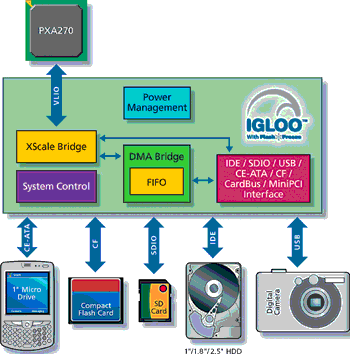

Handheld devices, such as smartphones, cameras, and MP3 players, are generally associated with a high-end embedded processor like the Marvell (formerly Intel) PXA or numerous ARM processors. These embedded processors need to work with one or more of the popular storage interfaces such as IDE, CE-ATA, SDIO, or CF. There is a pressing need to efficiently manage the interface for the storage devices by offloading the task from the processor to an FPGA. With IGLOO's ultra-low power capabilities, ease of use, and reprogrammability, it becomes an ideal choice. These devices can manage interfaces between the VLIO or AMBA bus and the different types of storage devices.

Power analysis tools

Actel provides comprehensive power analysis tools for IGLOO devices. These range from the Power Calculator (pre-netlist) tool for device comparison to post layout, in-depth analysis, and reporting tools.

The enhanced spreadsheet-based Power Calculator helps in analysing design implementation options for rapid 'what if' power analysis and design partitioning. Enhanced power reporting for low power Flash*Freeze mode, and all other operating modes, enables the designer to calculate and predict total system power consumption, summing up power consumed in each mode.

Actel's Libero integrated design environment (IDE) SmartPower tool provides netlist-based analysis capabilities. Power reports are broken down by net, gate, I/O, memory, clock, core static, instance, and power rail. A design-level power summary includes average switching activity, ambient temperature, and junction temperature readings. Actel power tools provide an accurate prediction that gives straightforward analysis of design options to help meet your system power budget.

Application support

Actel provides extensive application support for the IGLOO family of devices, including board-level schematics, IP cores, and development platforms for low power applications. Reference designs and documentation are available for cost-sensitive portable electronics, such as handheld and mobile storage, GPS, PDA, and smartphones as well as portable medical and industrial applications.

| Tel: | +27 11 315 8316 |

| Email: | [email protected] |

| www: | www.asic.co.za |

| Articles: | More information and articles about ASIC Design Services |

© Technews Publishing (Pty) Ltd | All Rights Reserved